## Math 230 Assembly Programming (AKA Computer Organization) Spring 2008

## **MIPS** Intro

Adapted from slides developed for: Mary J. Irwin PSU CSE331 Dave Patterson's UCB CS152

Smith Spring 2008

## MIPS - originally an acronym for Microprocessor without Interlocked Pipeline Stages)

Smith Spring 2008

```

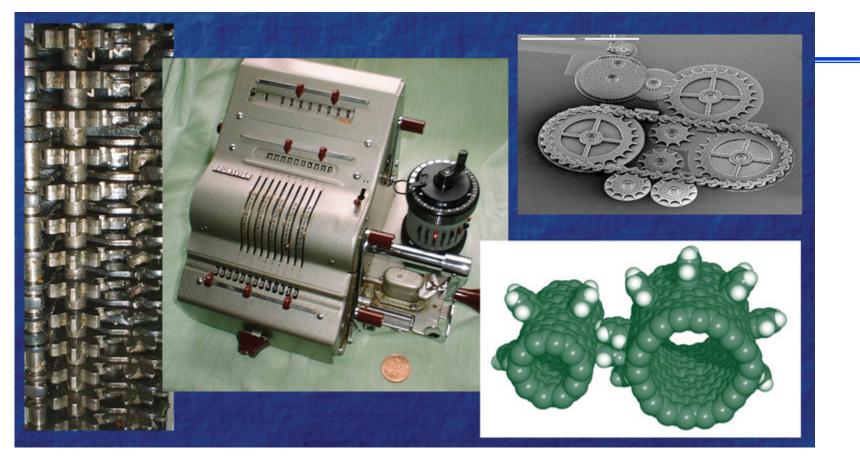

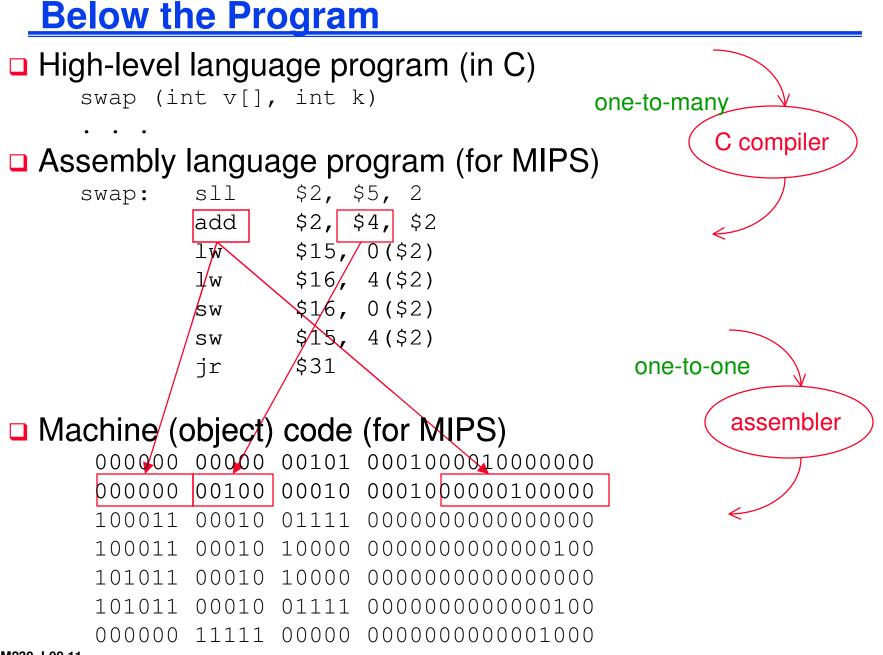

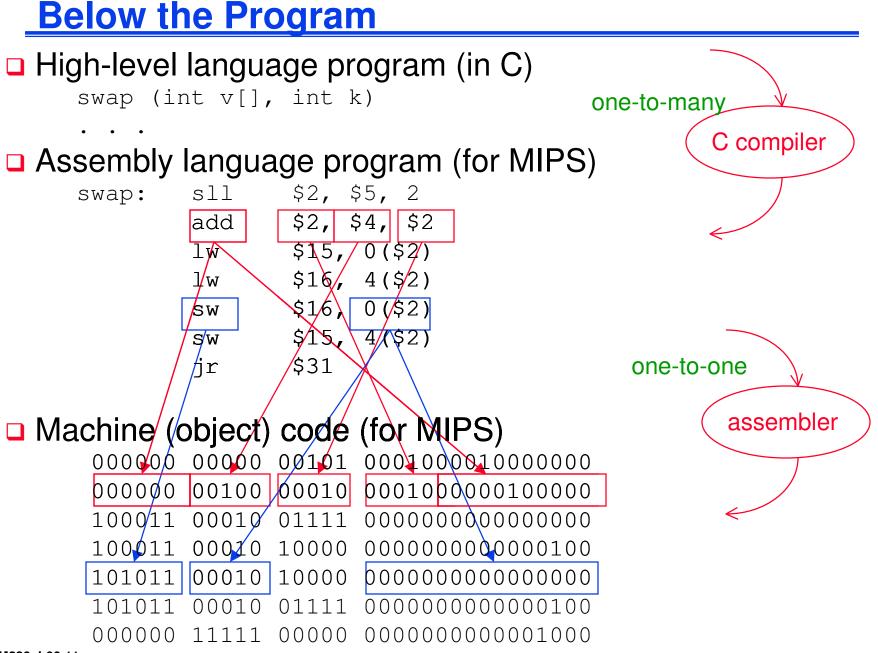

Below the Program

```

```

Below the Program

```

#### □ Machine (object) code (for MIPS)

000000 00000 00101 000100001000000 000000 00100 00010 000100000100000

M230 L09.5

. . .

Smith Spring 2008

#### Assembly language program (for MIPS)

| swap: | sll | \$2, \$       | 5 <b>,</b> 2    |

|-------|-----|---------------|-----------------|

|       | add | \$2, \$       | 54 <b>,</b> \$2 |

|       | lw  | \$15 <b>,</b> | 0(\$2)          |

|       | lw  | \$16,         | 4(\$2)          |

|       | SW  | \$16,         | 0(\$2)          |

|       | SW  | \$15 <b>,</b> | 4(\$2)          |

|       | jr  | \$31          |                 |

#### □ Machine (object) code (for MIPS)

000000 00000 00101 000100001000000 000000 00100 00010 000100000100000

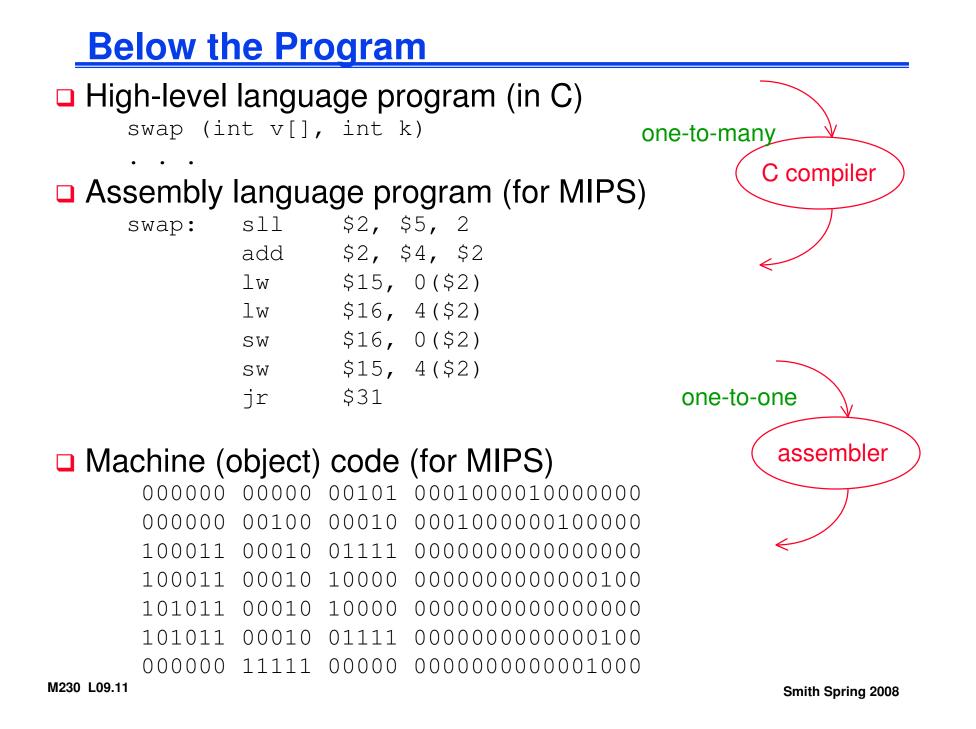

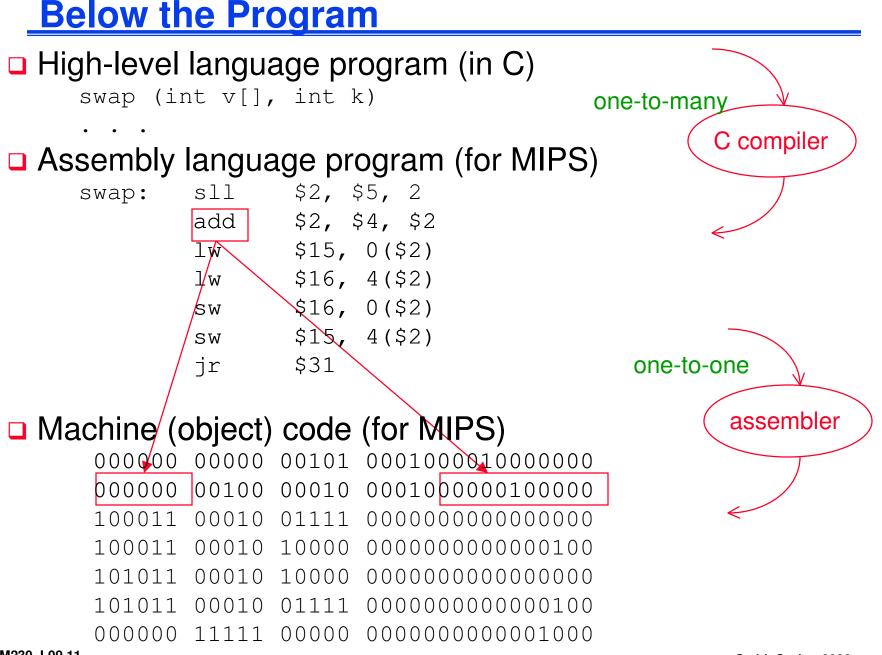

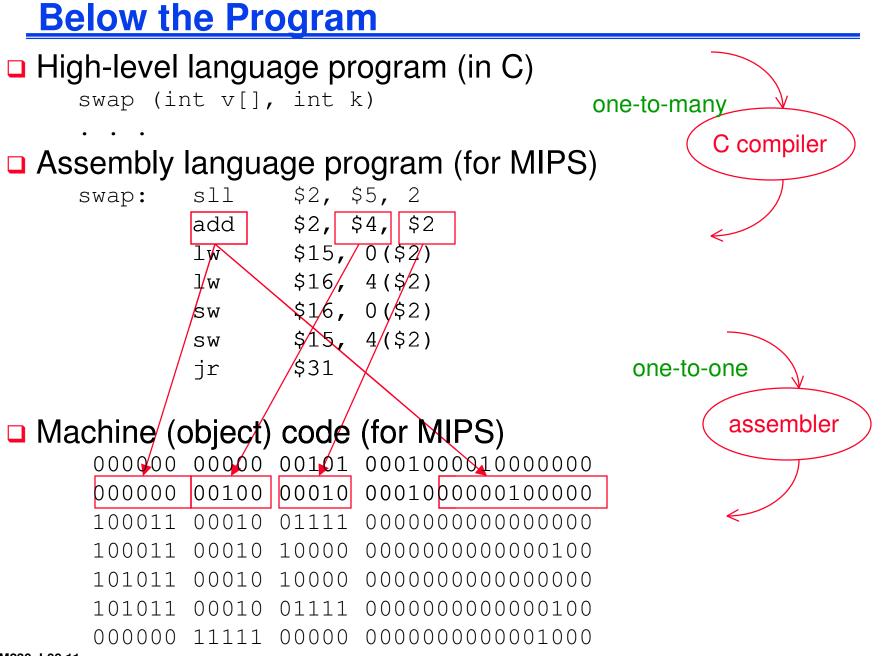

# Below the Program High-level language program (in C)

```

swap (int v[], int k)

{int temp;

temp = v[k];

v[k] = v[k+1];

v[k+1] = temp;

}

```

#### Assembly language program (for MIPS)

| swap: | sll | \$2, \$       | 5 <b>,</b> 2    |

|-------|-----|---------------|-----------------|

|       | add | \$2, \$       | 54 <b>,</b> \$2 |

|       | lw  | \$15 <b>,</b> | 0(\$2)          |

|       | lw  | \$16 <b>,</b> | 4(\$2)          |

|       | SW  | \$16 <b>,</b> | 0(\$2)          |

|       | SW  | \$15 <b>,</b> | 4(\$2)          |

|       | jr  | \$31          |                 |

#### Machine (object) code (for MIPS)

000000 00000 00101 000100001000000 000000 00100 00010 000100000100000

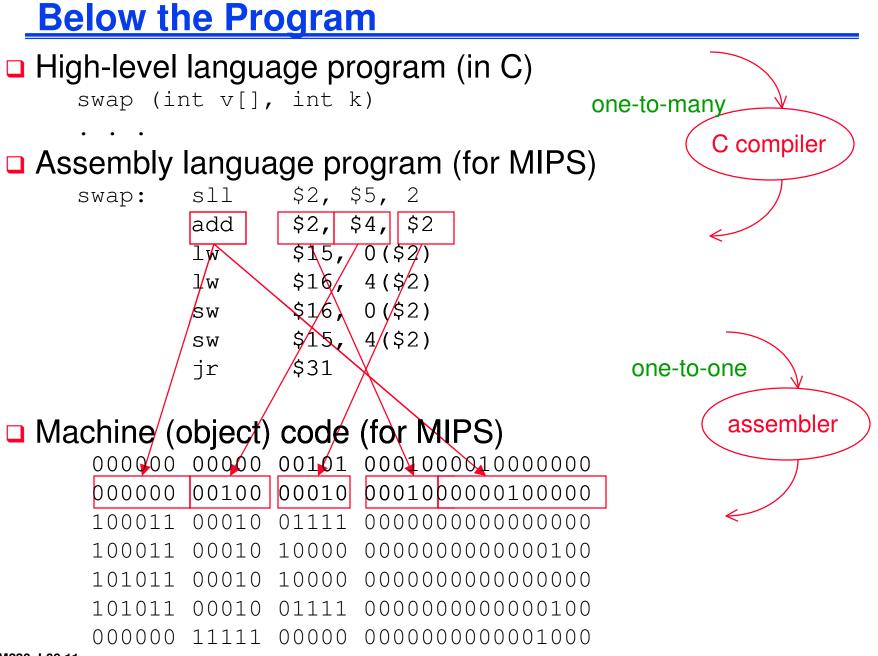

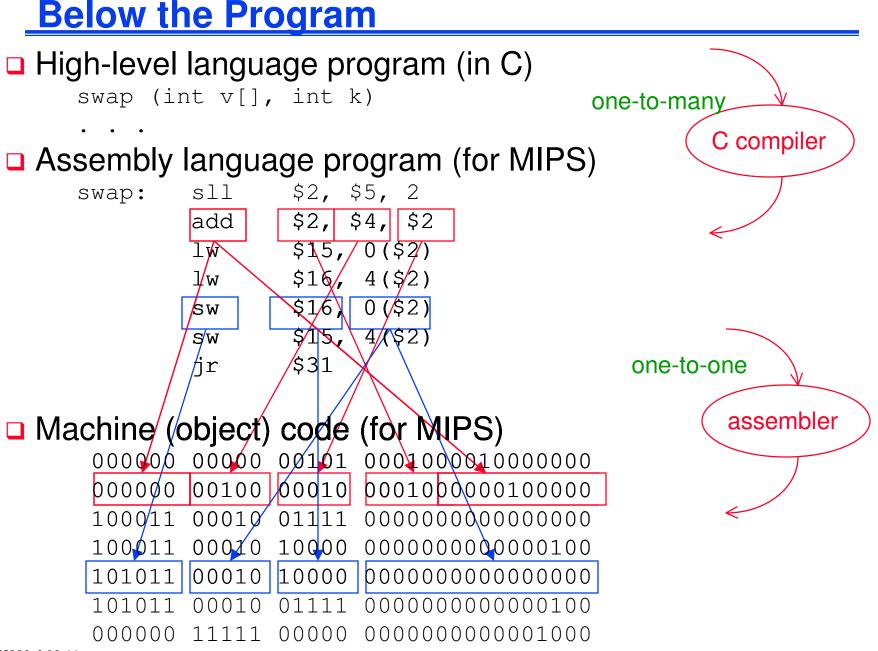

# Below the Program High-level language program (in C)

```

swap (int v[], int k)

{int temp;

temp = v[k];

v[k] = v[k+1];

v[k+1] = temp;

}

```

#### Assembly language program (for MIPS)

swap: sll \$2, \$5, 2

add \$2, \$4,\$2

lw \$15, 0(\$2)

lw \$16, 4(\$2)

sw \$16, 0(\$2)

sw \$15, 4(\$2)

jr \$31

#### Machine (object) code (for MIPS)

000000 00000 00101 000100001000000 000000 00100 00010 000100000100000 C compiler

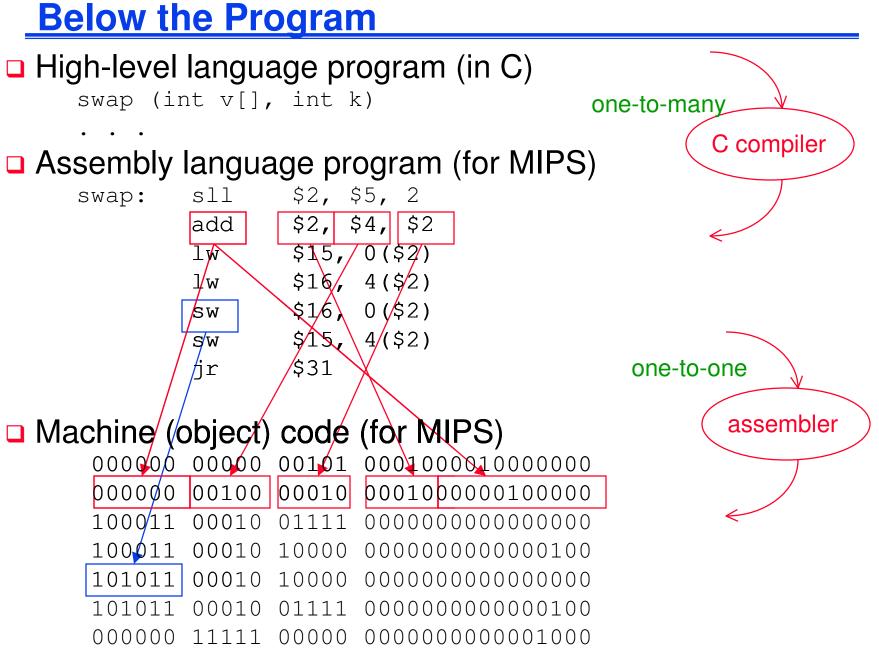

# Below the Program High-level language program (in C)

```

swap (int v[], int k)

{int temp;

temp = v[k];

v[k] = v[k+1];

v[k+1] = temp;

}

```

### Assembly language program (for MIPS)

swap: sll \$2, \$5, 2

add \$2, \$4,\$2

lw \$15, 0(\$2)

lw \$16, 4(\$2)

sw \$16, 0(\$2)

sw \$15, 4(\$2)

jr \$31

#### Machine (object) code (for MIPS)

00000000000001010001000010000000000000010000010000100000100000

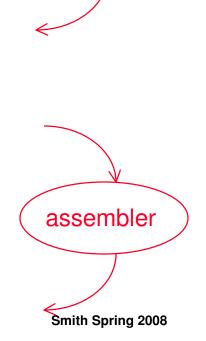

C compiler

Higher-level languages

Higher-level languages

• Allow the programmer to think in a more natural language and for their intended use (Fortran for scientific computation, Cobol for business programming, Lisp for symbol manipulation, ...)

Higher-level languages

- Allow the programmer to think in a more natural language and for their intended use (Fortran for scientific computation, Cobol for business programming, Lisp for symbol manipulation, ...)

- Improve programmer productivity more understandable code that is easier to debug and validate

#### Higher-level languages

- Allow the programmer to think in a more natural language and for their intended use (Fortran for scientific computation, Cobol for business programming, Lisp for symbol manipulation, ...)

- Improve programmer productivity more understandable code that is easier to debug and validate

- Improve program maintainability

#### Higher-level languages

- Allow the programmer to think in a more natural language and for their intended use (Fortran for scientific computation, Cobol for business programming, Lisp for symbol manipulation, ...)

- Improve programmer productivity more understandable code that is easier to debug and validate

- Improve program maintainability

- Allow programmers to be independent of the computer on which they are developed (compilers and assemblers can translate high-level language programs to the binary instructions of any machine)

#### Higher-level languages

- Allow the programmer to think in a more natural language and for their intended use (Fortran for scientific computation, Cobol for business programming, Lisp for symbol manipulation, ...)

- Improve programmer productivity more understandable code that is easier to debug and validate

- Improve program maintainability

- Allow programmers to be independent of the computer on which they are developed (compilers and assemblers can translate high-level language programs to the binary instructions of any machine)

- Emergence of optimizing compilers that produce very efficient assembly code optimized for the target machine

- As a result, very little programming is done today at the assembler level

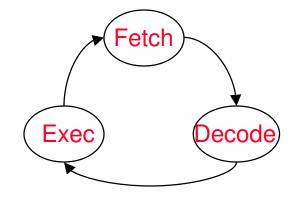

```

Machine Organization

```

- Capabilities and performance characteristics of the principal Functional Units (FUs)

- e.g., register file, ALU, multiplexors, memories, ...

Capabilities and performance characteristics of the principal Functional Units (FUs)

• e.g., register file, ALU, multiplexors, memories, ...

- The ways those FUs are interconnected

- e.g., buses

- Capabilities and performance characteristics of the principal Functional Units (FUs)

- e.g., register file, ALU, multiplexors, memories, ...

- The ways those FUs are interconnected

- e.g., buses

- Logic and means by which information flow between FUs is controlled

- Capabilities and performance characteristics of the principal Functional Units (FUs)

- e.g., register file, ALU, multiplexors, memories, ...

- The ways those FUs are interconnected

- e.g., buses

- Logic and means by which information flow between FUs is controlled

The machine's Instruction Set Architecture (ISA)

- Capabilities and performance characteristics of the principal Functional Units (FUs)

- e.g., register file, ALU, multiplexors, memories, ...

- The ways those FUs are interconnected

- e.g., buses

- Logic and means by which information flow between FUs is controlled

□ The machine's Instruction Set Architecture (ISA)

Register Transfer Level (RTL) machine description

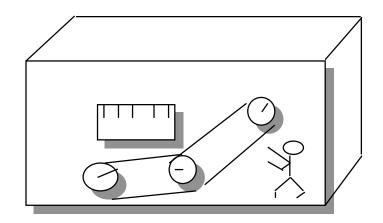

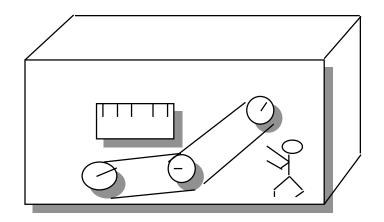

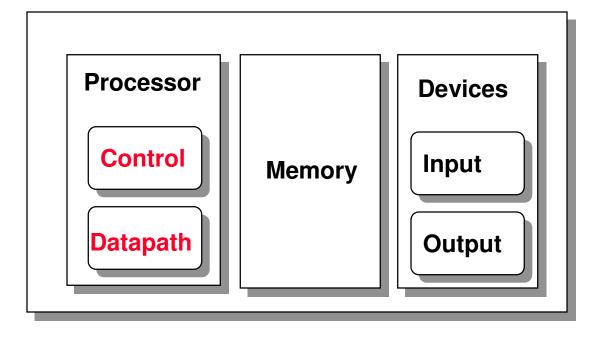

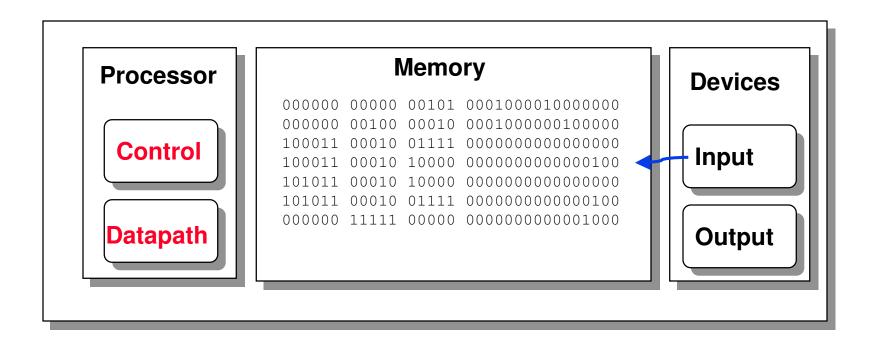

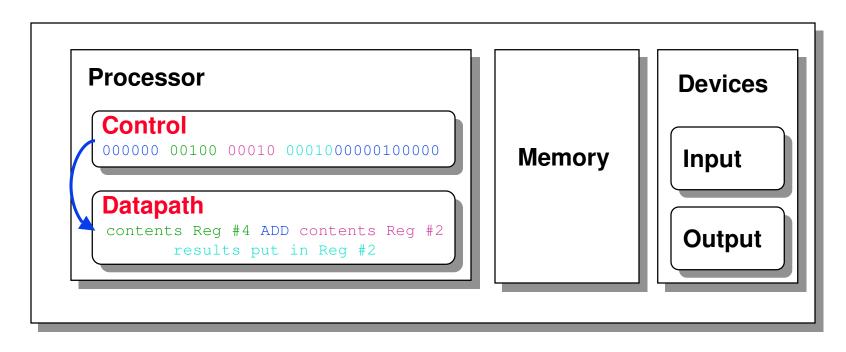

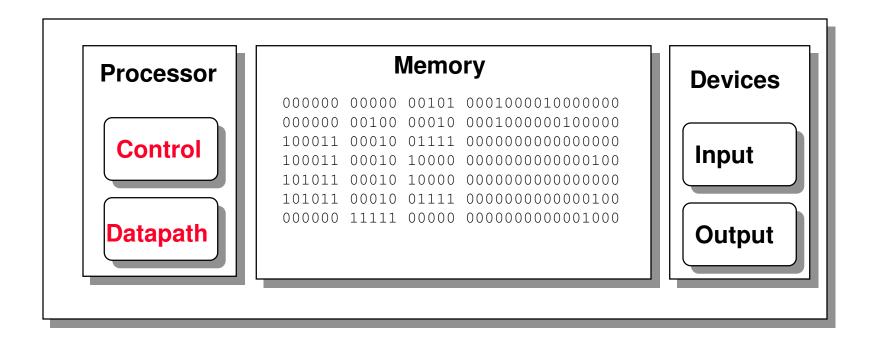

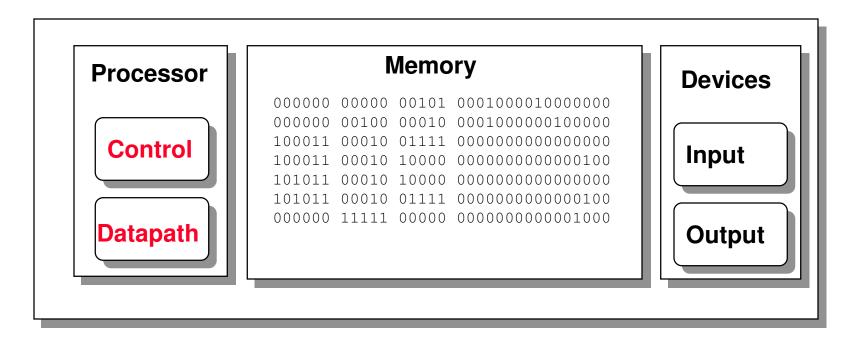

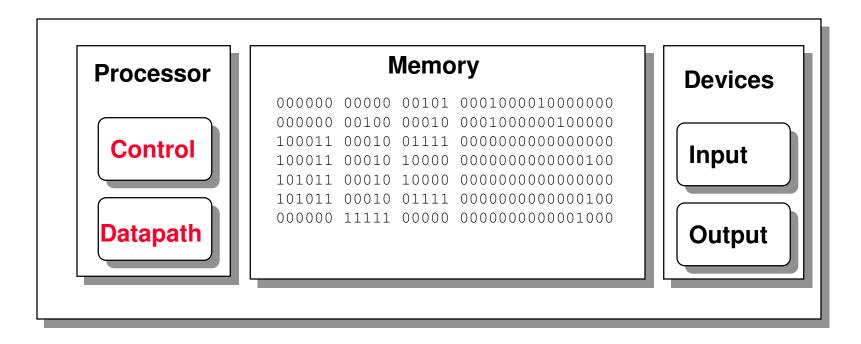

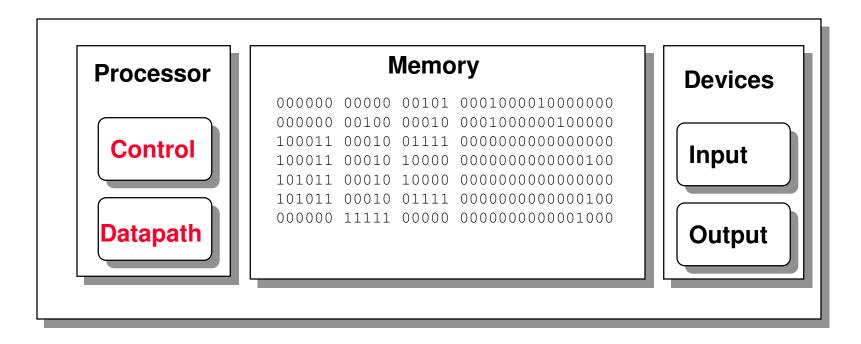

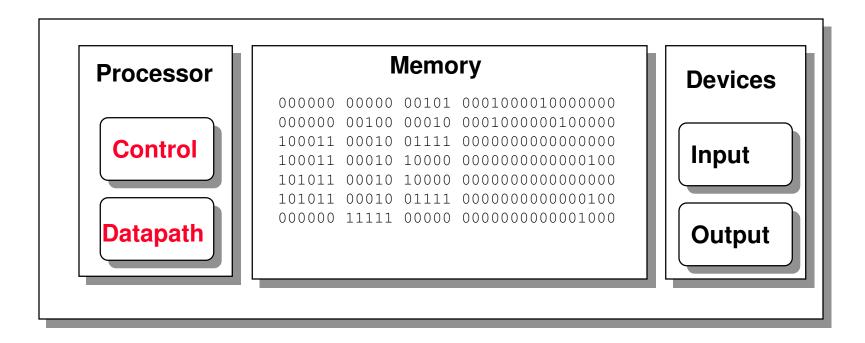

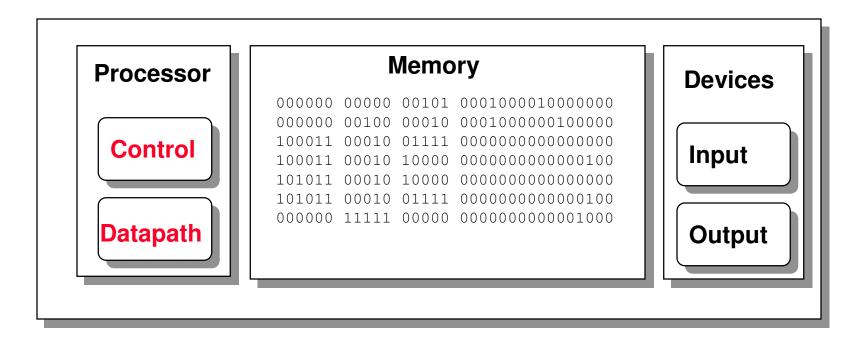

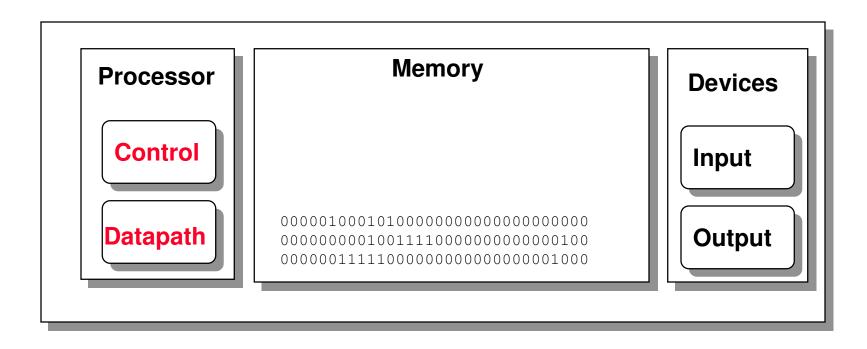

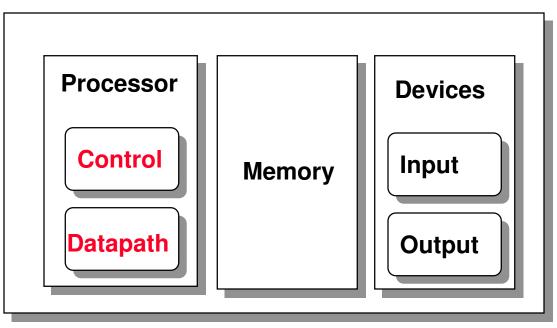

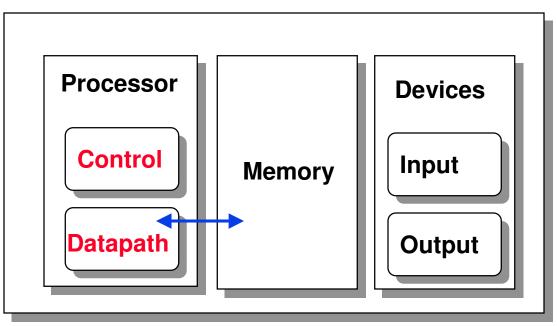

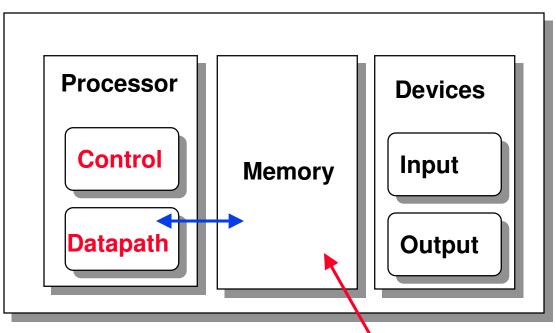

### **Major Components of a Computer**

## **Input Device Inputs Object Code**

000000 00000 00101 0001000010000000 000000 00100 00010 000100000100000 100011 00010 01111 000000000000000 100011 00010 10000 00000000000000000 101011 00010 10000 000000000000000 101011 00010 01111 00000000000000000 000000 11111 00000 00000000000000000 **Processor Devices** Control Input Memory Datapath Output

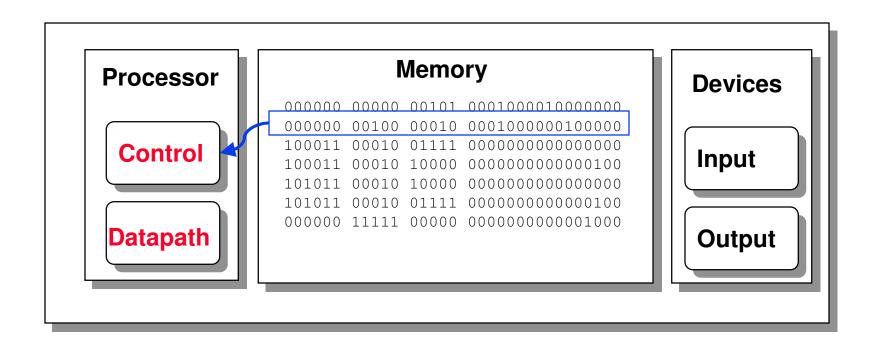

### **Object Code Stored in Memory**

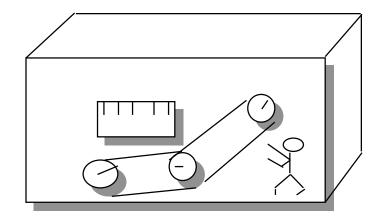

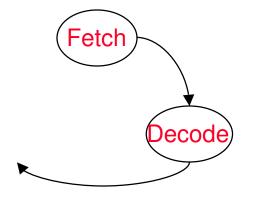

### **Processor Fetches an Instruction**

#### Processor fetches an instruction from memory

#### Where does it fetch from?

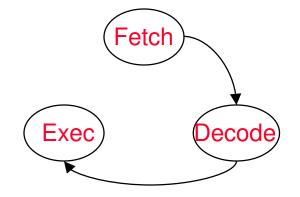

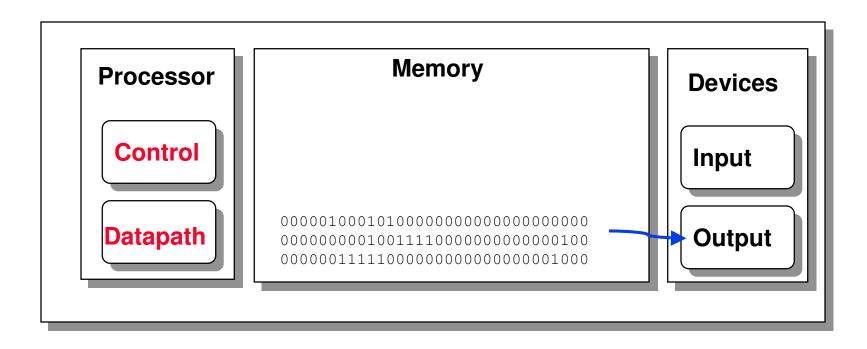

**Control Decodes the Instruction**

## Control decodes the instruction to determine what to execute

| Processor                             |        | Devices |

|---------------------------------------|--------|---------|

| Control 000000 00100 00010 0001000000 | Memory |         |

| Datapath                              |        |         |

|                                       |        | Output  |

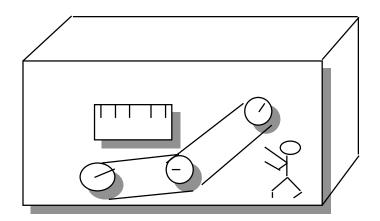

**Datapath Executes the Instruction**

## Datapath executes the instruction as directed by control

```

Processor Organization

```

## **Processor Organization**

#### Control needs to have the

- Ability to input instructions from memory

- Logic and means to control instruction sequencing

- Logic and means to issue signals that control the way information flows between datapath components

- Logic and means to control what operations the datapath's functional units perform

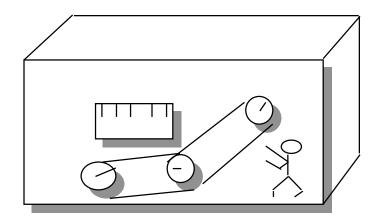

## **Processor Organization**

#### Control needs to have the

- Ability to input instructions from memory

- Logic and means to control instruction sequencing

- Logic and means to issue signals that control the way information flows between datapath components

- Logic and means to control what operations the datapath's functional units perform

#### Datapath needs to have the

- Components functional units (e.g., adder) and storage locations (e.g., register file) - needed to execute instructions

- Components interconnected so that the instructions can be accomplished

- Ability to load data from and store data to memory

## **Processor Organization**

#### Control needs to have the

- Ability to input instructions from memory

- Logic and means to control instruction sequencing

- Logic and means to issue signals that control the way information flows between datapath components

- Logic and means to control what operations the datapath's functional units perform

#### Datapath needs to have the

- Components functional units (e.g., adder) and storage locations (e.g., register file) - needed to execute instructions

- Components interconnected so that the instructions can be accomplished

- Ability to load data from and store data to memory

Where does it load and store from and to?

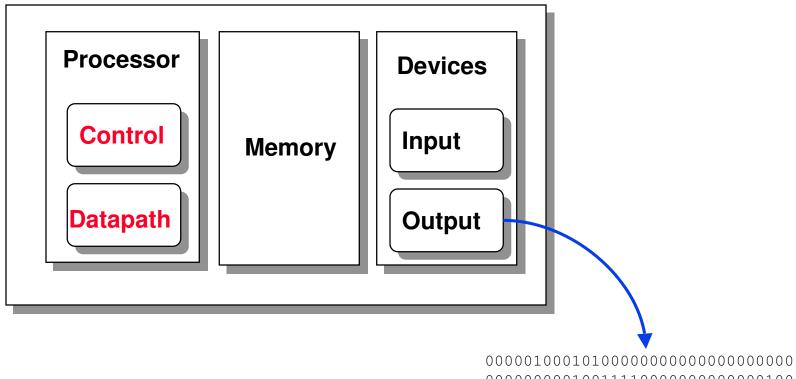

**Output Data Stored in Memory**

# At program completion the data to be output resides in memory

**Output Data Stored in Memory**

# At program completion the data to be output resides in memory

#### **Output Device Outputs Data**

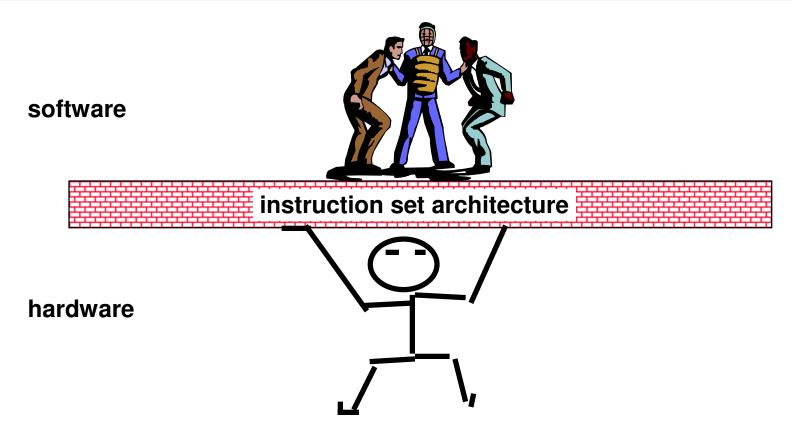

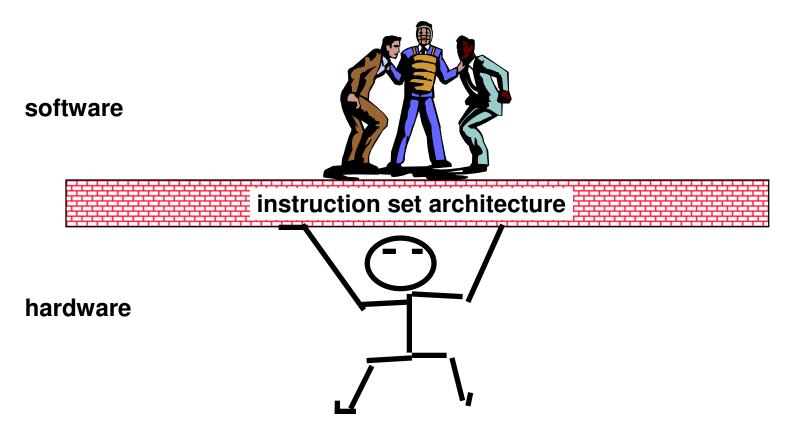

#### **The Instruction Set Architecture**

software

instruction set architecture

hardware

#### **The Instruction Set Architecture**

## The Instruction Set Architecture

# The interface description separating the software and hardware.

### **MIPS R3000 Instruction Set Architecture**

| 🗖 In | Instruction Categories |  |  |  |  |

|------|------------------------|--|--|--|--|

| •    | Load/Store             |  |  |  |  |

| •    | Computational          |  |  |  |  |

| •    | Jump and Branch        |  |  |  |  |

| •    | Floating Point         |  |  |  |  |

|      | - coprocessor          |  |  |  |  |

| •    | Memory Management      |  |  |  |  |

• Special

#### Registers

| R0 - R31 |  |

|----------|--|

| PC       |  |

| HI       |  |

| LO       |  |

#### **3** Instruction Formats: all 32 bits wide

| OP             | rs | rt | rd   | sa     | funct |

|----------------|----|----|------|--------|-------|

| ОР             | rs | rt | imme | ediate |       |

| OP jump target |    |    |      |        |       |

## **MIPS R3000 Instruction Set Architecture**

| Instruction Categories |                   |  |  |  |

|------------------------|-------------------|--|--|--|

| •                      | Load/Store        |  |  |  |

| •                      | Computational     |  |  |  |

| •                      | Jump and Branch   |  |  |  |

| •                      | Floating Point    |  |  |  |

|                        | - coprocessor     |  |  |  |

| •                      | Memory Management |  |  |  |

• Special

#### **Registers**

| R0 - R31 |

|----------|

| PC       |

| HI       |

| LO       |

#### **3** Instruction Formats: all 32 bits wide

| OP             | rs | rt | rd        | sa | funct |

|----------------|----|----|-----------|----|-------|

| ОР             | rs | rt | immediate |    |       |

| OP jump target |    |    |           |    |       |

**Q: How many already familiar with MIPS ISA?**

### **Assembly Language Instructions**

- Language of the machine

- More primitive than higher level languages e.g., no sophisticated control flow

- Very restrictive e.g., MIPS arithmetic instructions

- We'll be working with the MIPS instruction set architecture

- similar to other architectures developed since the 1980's

- used by NEC, Nintendo, Silicon Graphics, Sony, ...

Design goals: maximize performance, minimize cost, reduce design time, minimize memory space (embedded systems), minimize power consumption (mobile systems)

## **RISC - Reduced Instruction Set Computer**

#### RISC philosophy

- fixed instruction lengths

- load-store instruction sets

- limited addressing modes

- limited operations

- MIPS, Sun SPARC, HP PA-RISC, IBM PowerPC, Intel (Compaq) Alpha, ...

- Instruction sets are measured by how well compilers use them as opposed to how well assembly language programmers use them

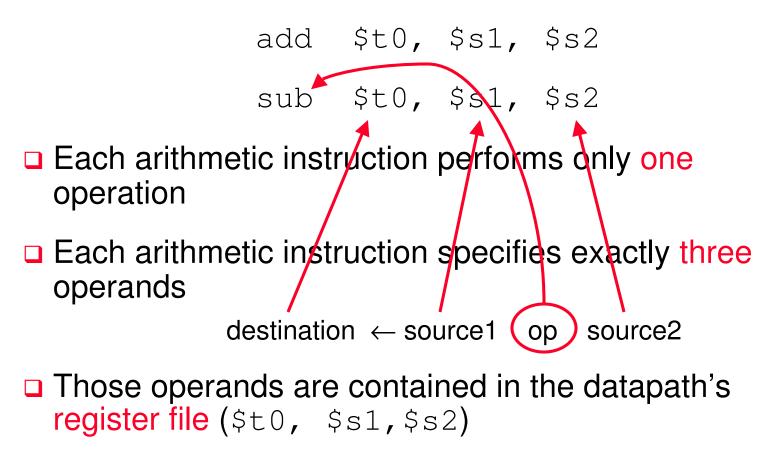

MIPS assembly language arithmetic statement

add \$t0, \$s1, \$s2 sub \$t0, \$s1, \$s2

- Each arithmetic instruction performs only one operation

- Each arithmetic instruction specifies exactly three operands

- Those operands are contained in the datapath's register file (\$t0, \$s1,\$s2)

- Operand order is fixed (destination first)

MIPS assembly language arithmetic statement

add \$t0, \$s1, \$s2

sub \$t0, \$s1, \$s2

- Each arithmetic instruction performs only one operation

- Each arithmetic instruction specifies exactly three operands

- Those operands are contained in the datapath's register file (\$t0, \$s1,\$s2)

- Operand order is fixed (destination first)

MIPS assembly language arithmetic statement

add \$t0, \$s1, \$s2

sub \$t0, \$s1, \$s2

- Each arithmetic instruction performs only one operation

- Each arithmetic instruction specifies exactly three operands

- Those operands are contained in the datapath's register file (\$t0, \$s1,\$s2)

- Operand order is fixed (destination first)

MIPS assembly language arithmetic statement

add \$t0, \$s1, \$s2

sub \$t0, \$s1, \$s2

- Each arithmetic instruction performs only one operation

- Each arithmetic instruction specifies exactly three operands

- Those operands are contained in the datapath's register file (\$t0, \$s1,\$s2)

- Operand order is fixed (destination first)

MIPS assembly language arithmetic statement

Operand order is fixed (destination first)

## **Compiling More Complex Statements**

Assuming variable b is stored in register \$s1, c is stored in \$s2, and d is stored in \$s3 and the result is to be left in \$s0, what is the assembler equivalent to the C statement

$$h = (b - c) + d$$

### **Compiling More Complex Statements**

Assuming variable b is stored in register \$s1, c is stored in \$s2, and d is stored in \$s3 and the result is to be left in \$s0, what is the assembler equivalent to the C statement

$$h = (b - c) + d$$

- Operands of arithmetic instructions must be from a limited number of special locations contained in the datapath's register file

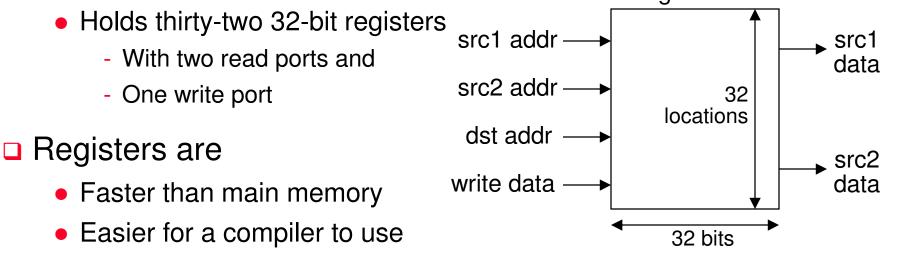

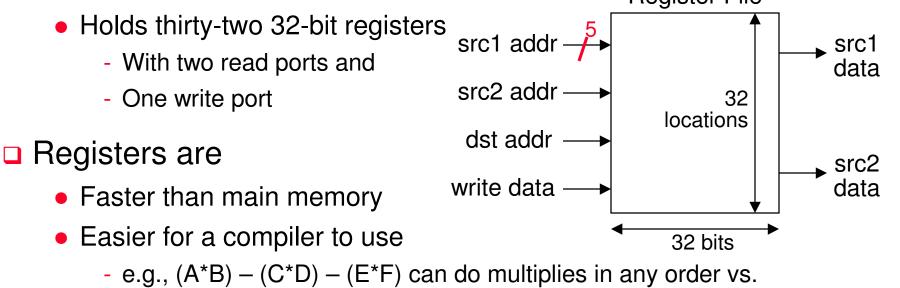

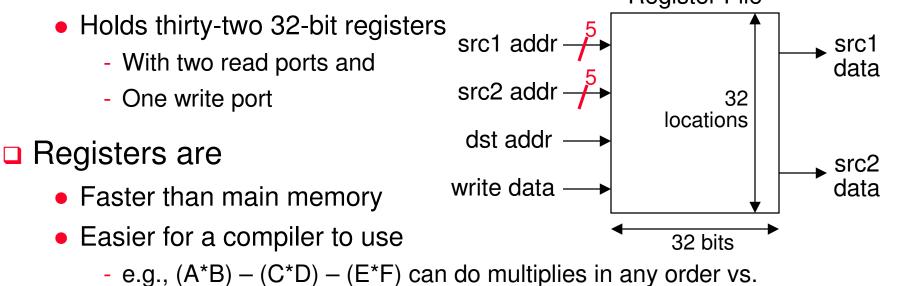

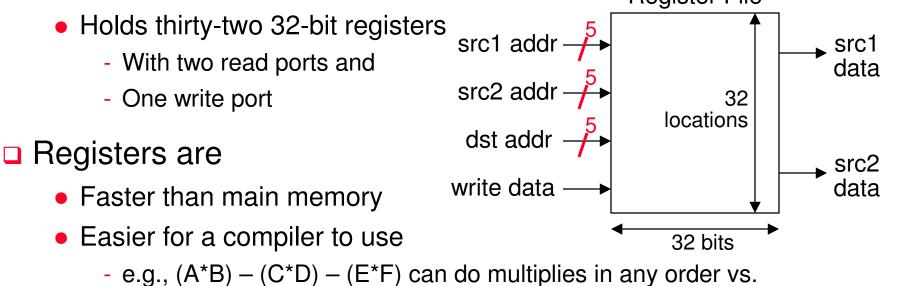

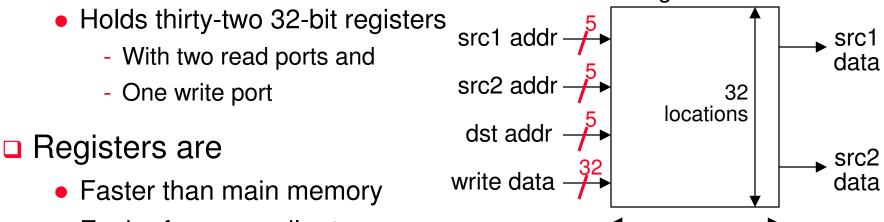

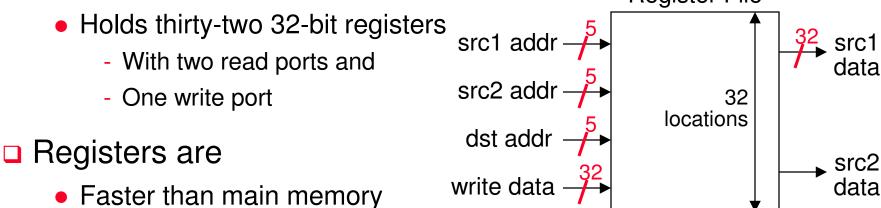

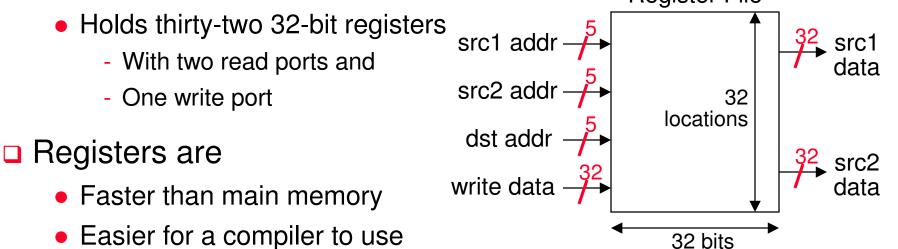

- Holds thirty-two 32-bit registers

- With two read ports and

- One write port

#### Registers are

- Faster than main memory

- Easier for a compiler to use

- e.g., (A\*B) (C\*D) (E\*F) can do multiplies in any order vs. stack

- Can hold variables so that

- code density improves (since register are named with fewer bits than a memory location)

Operands of arithmetic instructions must be from a limited number of special locations contained in the datapath's register file

Register File

e.g., (A\*B) – (C\*D) – (E\*F) can do multiplies in any order vs. stack

- Can hold variables so that

- code density improves (since register are named with fewer bits than a memory location)

#### Register addresses are indicated by using \$

than a memory location)

Operands of arithmetic instructions must be from a limited number of special locations contained in the datapath's register file

Register File

• Can hold variables so that

stack

- code density improves (since register are named with fewer bits than a memory location)

Operands of arithmetic instructions must be from a limited number of special locations contained in the datapath's register file Register File

Can hold variables so that

stack

- code density improves (since register are named with fewer bits than a memory location)

Operands of arithmetic instructions must be from a limited number of special locations contained in the datapath's register file

Register File

• Can hold variables so that

stack

- code density improves (since register are named with fewer bits than a memory location)

Operands of arithmetic instructions must be from a limited number of special locations contained in the datapath's register file Register File

- Easier for a compiler to use

- e.g., (A\*B) (C\*D) (E\*F) can do multiplies in any order vs. stack

- Can hold variables so that

- code density improves (since register are named with fewer bits than a memory location)

#### Register addresses are indicated by using \$

32 bits

Operands of arithmetic instructions must be from a limited number of special locations contained in the datapath's register file Register File

- Easier for a compiler to use

- e.g., (A\*B) (C\*D) (E\*F) can do multiplies in any order vs. stack

- Can hold variables so that

- code density improves (since register are named with fewer bits than a memory location)

#### Register addresses are indicated by using \$

32 bits

Operands of arithmetic instructions must be from a limited number of special locations contained in the datapath's register file Register File

- e.g., (A\*B) (C\*D) (E\*F) can do multiplies in any order vs. stack

- Can hold variables so that

M230 L09.32

- code density improves (since register are named with fewer bits than a memory location)

## **Naming Conventions for Registers**

| 0  | <pre>\$zero constant 0 (Hdware)</pre> |

|----|---------------------------------------|

| 1  | <b>\$at reserved for assembler</b>    |

| 2  | \$v0 expression evaluation &          |

| 3  | \$v1 function results                 |

| 4  | \$a0 arguments                        |

| 5  | \$a1                                  |

| 6  | \$a2                                  |

| 7  | \$a3                                  |

| 8  | \$t0 temporary: caller saves          |

|    | (callee can clobber)                  |

| 15 | \$t7                                  |

| 16 | \$s0 callee saves                       |

|----|-----------------------------------------|

|    | (caller can clobber)                    |

| 23 | \$s7                                    |

| 24 | \$t8 temporary (cont'd)                 |

| 25 | \$t9                                    |

| 26 | <b>\$k0</b> reserved for OS kernel      |

| 27 | \$k1                                    |

| 28 | \$gp pointer to global area             |

| 29 | \$sp stack pointer                      |

| 30 | \$fp frame pointer                      |

| 31 | <pre>\$ra return address (Hdware)</pre> |

## **Registers vs. Memory**

Arithmetic instructions operands must be registers, — only thirty-two registers provided

- Compiler associates variables with registers

- What about programs with lots of variables?

## **Registers vs. Memory**

Arithmetic instructions operands must be registers, — only thirty-two registers provided

- Compiler associates variables with registers

- What about programs with lots of variables?

## **Registers vs. Memory**

Arithmetic instructions operands must be registers, — only thirty-two registers provided

- Compiler associates variables with registers

- What about programs with lots of variables?

### **Accessing Memory**

# MIPS has two basic data transfer instructions for accessing memory

|    |       |         | (assume \$s3 holds 24 <sub>10</sub> ) |

|----|-------|---------|---------------------------------------|

| SW | \$t0, | 8(\$s3) | #store word to memory                 |

| lw | \$t0, | 4(\$s3) | #load word from memory                |

□ The data transfer instruction must specify

- where in memory to read from (load) or write to (store) memory address

- where in the register file to write to (load) or read from (store) register destination (source)

- The memory address is formed by summing the constant portion of the instruction and the contents of the second register

**Accessing Memory**

MIPS has two basic data transfer instructions for accessing memory

- 28

1w \$t0, 4(\$s3) #load word from memory

- sw \$t0, 8(\$s3) #store word to memory

(assume \$s3 holds 24<sub>10</sub>)

□ The data transfer instruction must specify

- where in memory to read from (load) or write to (store) memory address

- where in the register file to write to (load) or read from (store) register destination (source)

- The memory address is formed by summing the constant portion of the instruction and the contents of the second register

**Accessing Memory**

MIPS has two basic data transfer instructions for accessing memory

- 28 lw \$t0, 4(\$s3) #load word from memory

- sw \$t0, 8(\$s3) #store word to memory 32 (assume \$s3 holds 24<sub>10</sub>)

□ The data transfer instruction must specify

- where in memory to read from (load) or write to (store) memory address

- where in the register file to write to (load) or read from (store) register destination (source)

- The memory address is formed by summing the constant portion of the instruction and the contents of the second register

| Category   | Instr      | Op Code  | Example              | Meaning                 |

|------------|------------|----------|----------------------|-------------------------|

| Arithmetic | add        | 0 and 32 | add \$s1, \$s2, \$s3 | \$s1 = \$s2 + \$s3      |

| (R format) | subtract   | 0 and 34 | sub \$s1, \$s2, \$s3 | \$s1 = \$s2 - \$s3      |

| Data       | load word  | 35       | lw \$s1, 100(\$s2)   | \$s1 = Memory(\$s2+100) |

| transfer   | store word | 43       | sw \$s1, 100(\$s2)   | Memory(\$s2+100) = \$s1 |

| (I format) |            |          |                      |                         |